International Journal of Engineering & Technology, 7 (4) (2018) 2291-2297

# International Journal of Engineering & Technology

Website: www.sciencepubco.com/index.php/IJET doi: 10.14419/ijet.v7i4.9684 **Research paper**

# Operating conditions analysis of memristor model

N Khadar Basha 1\*, Dr. T Ramashri 2

<sup>1</sup> Research scholar, Department of Electronics and Communication Engineering, S V University, Tirupati, A.P., India

<sup>2</sup> Professor, Department of Electronics and Communication Engineering, S V University, Tirupati, A.P., India

\*Corresponding author E-mail: nkhadar@gmail.com

## Abstract

The two terminal, fourth basic circuit element, memristor acts as nonlinear resistor with built-in memory functionality. Memristor has many advantages like non-volatile, no leakage current, Even when the power supply turn off, it retains its memory and typically apparent only at small scale. It shows significant effect in digital circuit application because it stores logic values without power consumption and logic values are measured based on the memristance value. Memristor is a class of non-volatile memory storage and is suitable for nanoscale memory applications. It is considered one of the most promising technology to implement memory and logic operations in a single cell. In this technology stored information is calculated as a low resistive state (LRS) and high resistive state (HRS). A detailed operating conditions of tunneling modulation model of memristor is studied and analyzed the operating frequency and voltage ranges in this paper. Switching behavior is measured based on the transition time of memristance change from one state to another state at different working frequencies.

Keywords: High Resistive State (HRS); Low Resistive State (LRS); Memristance; Nonlinear; Switching behavior.

## 1. Introduction

Mathematical formulation of forth fundamental element as memristor has proposed by Leon Chua in 1971[1], and later this concept was extended to memristive devices and systems [2]. Chua derived formulae for memristor from physical quantities and noticed the missing link between flux and charge as shown in figure 1, describing the element as memristor. He characterized memristor in term of flux and charge instead of voltage and current. The charge and flux are time integral of current and voltage respectively. Practical realization of titanium dioxide based memristor was announced by HP labs in 2008 [3], proved the feasibility of memristor by publication several paper and patients on memristors. Since then more researchers focus to exploit new possibilities for developing memristor by utilizing variable resistance as state variable. The researchers developed other types of memristive devices: spin memristive systems [4]; manganite memristive systems [5] and polymeric memristors [6]. Since then memristor is hot topic of research around the memristive characteristics, simulations and memristive applications. The memristor has new opportunities in neuromarphic applications and large memory applications at nanoscale [7] - [13].

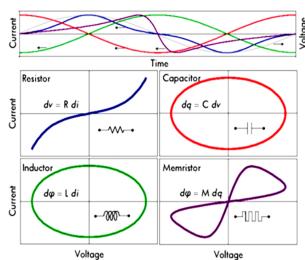

The relationship between physical quantities and basic electrical circuits are described as shown in figure 2. The resistor dissipate energy, capacitor store energy in electric field, inductor store energy in magnetic field and the memristor store information. The important characteristics and features for memristors: 1) A two terminal circuit element 2) An AC element, not DC 3) No storage of energy 4) Pinched hysteresis characteristics in the V-I plane 5) Positive or negative memristance 6) Nonlinear charge - flux curve 7) Frequency-dependent memristance and Low frequency property 8) Apparent only at small scales 9) non-volatile and no leakage current.

Fig. 1: Relationship between Voltage and Current for Basic Circuit Element

Memristors can create a new pathway for designing circuits at nanoscale because of its massive parallelism, scalability, fault tolerance and failure tolerance. Memristor technology is used to design stable memory due to its non-volatile state retention characteristics. Memristors built in sense of history used to design memory and logic circuits. They are so many memristor models are proposed so far by using constituent equations or flux-charge relationship in the circuit simulation tools like SPICE, Verilog, Spectre etc. based on the boundary conditions incorporation in HP model such as window functions, piecewise linear charge flux method and oxygen vacancy drift model. They had some limitations: 1) some models cannot included threshold voltages for read/write mode in RRAM devices [14]-[20]. 2) Some device

model can hold its memductance at boundary values forever regardless applied external voltage/current [14], [16], [18], [21] - [22]. 3) Although some models overcame the boundary backing problem [23]-[26]. 4) Some models are highly restricted to particular devices switching characteristics and not suitable for diverse device switching mechanisms [27]-[29].

## 2. Memristor

#### 2.1. Theory of memristor

The Two terminal element memristor is related to the two physical quantities of charge and flux. The fallowing equation can be obtain by assuming the flux ( $^{\circ}$ ) is a function of charge (q).

$$\varphi = f(q) \tag{1}$$

We know the differential equations of the charge and flux as shown in equations (2) and (3).

$$dq = idt (2)$$

$$d\varphi = vdt \tag{3}$$

From the above equations

$$v = \frac{d\varphi}{dt} = \frac{d\varphi}{dq}\frac{dq}{dt} = \frac{d\varphi}{dq}\dot{i}$$

(4)

The ratio between flux and charge is constant then it exhibit constant resistant according to ohms law and if the relationship between them is nonlinear it exhibit memristance as the property of memristor.

$$v = M(q)i (5)$$

$$M\left(q\right) = \frac{d\,\varphi}{dq}\tag{6}$$

By using SPICE simulator, we test the simulation results of our model for different working condition along with hysteresis property for various frequencies.

We the charge and flux are time integrals of the current and voltage as shown in equations (7) and (8).

$$q(t) = \int_{0}^{t} i(\tau)d(\tau) \tag{7}$$

$$\varphi(t) = \int v(\tau)d(\tau) \tag{8}$$

By substituting the above two equation in (1), the obtained equation is

$$\int i(\tau)d(\tau) = f\left(\int v(\tau)d(\tau)\right) \tag{9}$$

This equation implies that the memristor is a device whose relationship between the voltage and current is nonlinear.

## 2.2. HP memristor

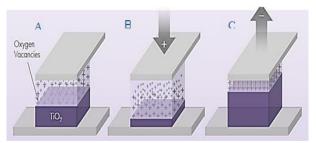

The memristor fabrication process first revealed by the HP labs. They fabricated the memristor by using titanium dioxide sandwiched in between the two platinum electrodes as shown in figure 2. The titanium dioxide has two layers, one layer is doped with oxygen vacancies and another is undoped. The doped layer plays major role in the operation of memristor it acts as the conductor and undoped layer act as insulator. Depends on the applied voltage the boundary between the doped and undoped layer can moves. The doped region consists of positive ions due to the deficiency of

oxygen. The total resistance of memristor is considered as the sum of doped and undoped region memristance. In general due to the conduction property of doped region it has less resistance. The undoped region has high resistance because the titanium dioxide has high resistance. The total resistance of memristor is depends on the boundary drift. The small change in the ions has less contribution of boundary and change of resistance.

When the positive voltage is applied on the positive terminal of the device, the positive ions drift to words the undoped region due to the repulsion of charge and applied voltage hence the boundary drift towards the undoped region (the width of doped region is increases and undoped region width is reduced) as shown in figure 2(b). For negative applied voltage, the oxygen vacancies are attracted by the negative voltage terminal hence all ions are at upper terminal hence the width of doped region is decreases as shown in figure 2(c). The width of the doped region is inversely proportional to resistance of the memristance.

Fig. 2: Physical Structure of Memristor.

#### 2.3. Electrical characteristics

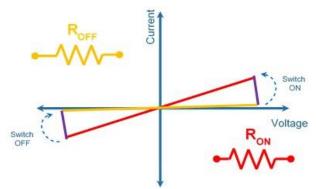

Fig. 3: Switching Characteristics of Memristor.

The memristor can store information in form of resistance. High resistance state is considered as logic 0 or OFF state and low resistance state is considered as logic 1 or ON state. The switching operation depend on the boundary drift. The V-I characteristics of memristor form hysteresis curve, it represent the storage of information. At origin the curve is pinched i.e at zero voltage it has no current flow. When the device is initially in off state and applying the positive voltage there is no current flow until a particular voltage then it change its state from ON to OFF state, afterwards the current is directly proportional to the applied voltage as shown in red colour in the figure 3. When the applied voltage reaches negative threshold then only the memristor changes it state from ON state to OFF, and it hold in this stage until the applied voltage reaches the positive threshold, the OFF state of memristor is

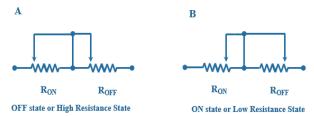

Fig. 4: OFF State and ON State Internal Resistance of Memristor.

Shown in figure with orange color. Based on this switching characteristics, the memristor is used as switch. The ON state or High Resistance State (HRS) and OFF state or Low Resistance State internal resistance are observed as shown in figure 4(A) and 4(B) respectively.

# 3. Operating conditions of memristor model

We conduct experiment with the memristor SPICE model proposed in [30] to analyses the working conditions of memristor by calling memristor SPICE model as a sub circuit in LTspice simulation tool. We test the memristor under various voltages and frequencies and analyses the switching behavior by calculating the transient time.

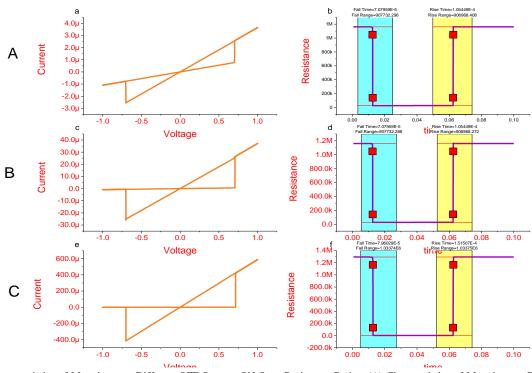

We start analysis with different OFF state to ON state resistance values by applying 1v sinusoidal voltage signal at 1hz frequency and observe the V I characteristics as below figure 5. The V-I characteristics of memristor with  $R_{\text{OFF}}\!\!=\!\!2K\Omega$  and  $R_{\text{ON}}\!\!=\!\!500\Omega$  as shown in figure 5(A), as the resistance is low then it has less number of oxygen vacancies hence the conduction of current is less as shown in the V-I characteristics. The V-I characteristics are became stronger at  $R_{\text{OFF}}\!\!=\!\!5K\Omega$  and  $R_{\text{ON}}\!\!=\!\!200\Omega$  as shown in figure 5(B). as the OFF state resistance or ratio of OFF state to ON state increases then the hysteresis characteristics of memristor becomes stronger and thus better switching characteristics occurs as shown in figure 5(c). As increasing the OFF state resistance to ON state resistance then lobe area increases. As

Fig. 5: V-I Characteristics of Memristors at Different OFF State to ON State Resistance Ratios. (A) Characteristics of Memristor at  $R_{OFF}$ =2K  $\Omega$  And  $R_{ON}$ =500 $\Omega$  (B) Characteristics of Memristor at  $R_{OFF}$ =5K  $\Omega$  and  $R_{ON}$ =200 $\Omega$  (C) Characteristics of Memristor at  $R_{OFF}$ =15K  $\Omega$  and  $R_{ON}$ =100 $\Omega$

Shown in figure 5(A), the variation of current and resistance with respect to the voltage and time are observed as shown in the figure 5

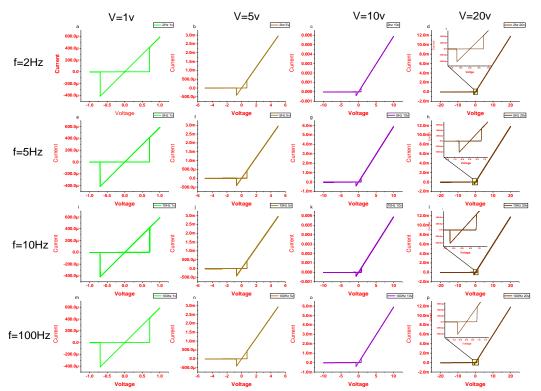

The hysteresis characteristics of memristor become stronger as the applied voltage increases and the model can be work for a particular voltage and after this range the memristor is not able to hold its state i.e. the right boundary of memristor deteriorates as increasing of the further more voltage. This gives the operating voltage of memristor. The operating voltage of memristor also depends on the applied voltage and aslo signal frequency. Now we start analysis for finding operating voltage upto 20v at different frequencies. From the simulation results as shown below, the model working fine without boundary deteriorate at 1 to 20 volts of input sinusoi-

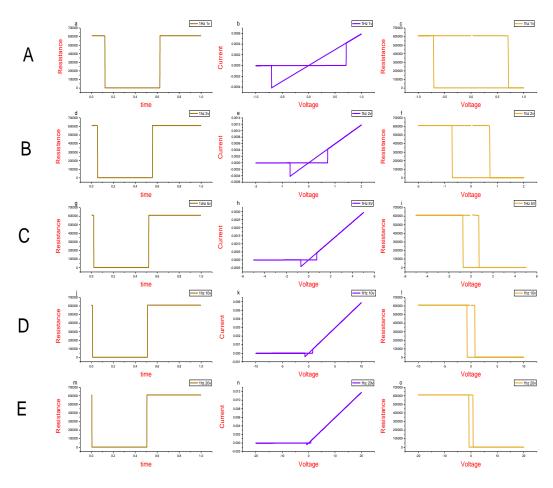

dal signal at the frequencies of 1 to 100Hz as shown in figure 6 and 7. The figure 6 shows the simulation results of memristor characteristics at 1Hz frequency with applied votages of 1v, 2v, 5v, 10v and 20v. The figure 7 shows the simulation results of memristor at 2Hz, 5Hz, 10Hz, and 100Hz frequencies and different applied voltages. In the above the simulations results the switching boundary is not get deteriorates. The switching characteristics occurs at threshold voltages and becomes stronger as the voltage is increases from 1v to 20v of input signal. As the frequency increases then the V I characteristics lobe area increases and the transient time also decreases.

$\textbf{Fig. 6:} \ Characteristics \ of \ Memristor \ at \ 1Hz \ Frequency \ with \ Different \ Input \ Voltages \ (A) \ 1V \ (B) \ 2V \ (C) \ 5V \ (D) \ 1010V \ (E) \ 20V.$

Fig 7: V-I Characteristics of Memristor at Different Voltage and Frequencies (2Hz, 5Hz, 10Hz and 100Hz).

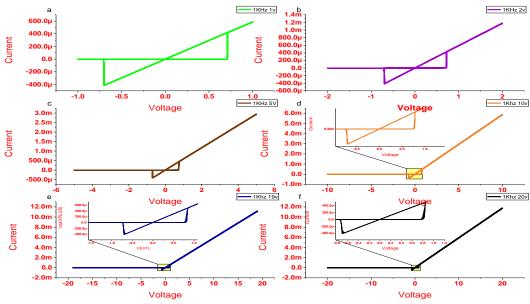

Fig. 8: V-I Characteristics of Memristor at 1 KHZ Frequency, Different Voltages (1V, 2V, 5V, 10V, 19V, 20V).

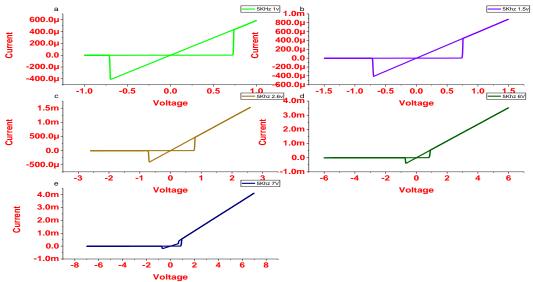

Fig. 9: V-I Characteristics of Memristor at 5 KHZ Frequency, Different Voltages (1V, 1.5V, 2.6V, 6V, 7V).

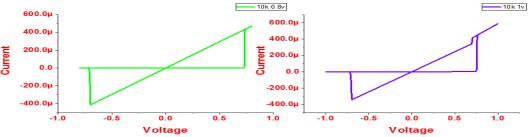

Fig. 10: V-I Characteristics of Memristor at 10 KHZ and Different Voltages (0.8V, 1V).

At the frequency 1Khzs, when the input signal voltage is increases then the switching characteristics occurs up to particular voltage 10v, after that voltage the right boundary deteriorates as shown in figure 8. Hence the operating voltage of memristor at 1 KHz is 0.7v-9v. At the frequency 5 KHz, the operating voltage of memristor is 0.7v-6v, above the 6v of applied voltage the boundary deteriorates as shown in figure 9. As the frequency increases the boundary get deteriorates even at very low voltages as shown in figure 10, hence the operating voltage of memristor at 10 KHz is 0.7v-0.9v. All the above results shows that the memristor model works at low frequencies over wide voltage range and at high frequencies, it operates very less voltage ranges.

The memristor works as a switch by applying suitable switching voltage it change it state from one state to another state (OFF to ON and ON to OFF). Actually, it take a certain amount of transition time to change its state. In case of memristor, the state change measured based on the time taken to change in resistance from Low Resistance State (LRS) to High Resistance State (HRS) and vice versa. The rise time and fall time are calculated based on resistance states. This time delays depends on the applied voltage and frequencies, hence we calculated the rise and fall times are calculated at different voltages and frequencies as shown in table 1 and 2. As the voltage and frequency of applied signal increases gradually then the rise time and fall time are decreases, hence the

switching characteristics become stronger as the applied voltage and frequency increases.

Table 1: Rise Time of Memristor at Various Operating Voltages and Frequencies

| Frequency/<br>Applied voltage | f=1 Hz   | 2 Hz     | 5 Hz     | 10 Hz    | 50 Hz    | 100 Hz   | 1 KHz    | 10 KHz              |

|-------------------------------|----------|----------|----------|----------|----------|----------|----------|---------------------|

| 1v                            | 0.00149  | 2.747e-4 | 2.015e-4 | 1.487e-4 | 9.418e-5 | 8.244e-5 | 1.305e-6 | 9.271e-7 at<br>0.8v |

| 2v                            | 0.00110  | 1.865e-4 | 1.357e-4 | 1.099e-4 | 7.869e-5 | 7.223e-5 | 1.081e-6 |                     |

| 5v                            | 8.768e-4 | 1.333e-4 | 1.024e-4 | 8.747e-5 | 7.029e-5 | 6.705e-5 | 8.828e-7 |                     |

| 10v                           | 7.759e-4 | 1.121e-4 | 8.747e-5 | 7.796e-5 | 6.699e-5 | 6.513e-5 |          |                     |

| 20v                           | 7.169e-4 | 9.151e-5 | 7.788e-5 | 7.169e-5 | 6.508e-5 | 6.402e-5 |          |                     |

Table 2: Fall Time at Different Frequencies by Varying Applied Voltage

| Frequency/<br>Applied voltage | f=1 Hz   | 2 Hz     | 5 Hz     | 10 Hz    | 50 Hz    | 100 Hz   | 1 KHz    | 10 KHz              |

|-------------------------------|----------|----------|----------|----------|----------|----------|----------|---------------------|

| 1v                            | 0.00155  | 2.918e-4 | 2.112e-4 | 1.562e-4 | 9.753e-5 | 8.449e-5 | 1.528e-6 | 9.418e-7 at<br>0.8v |

| 2v                            | 0.00114  | 1.978e-4 | 1.424e-4 | 1.522e-4 | 8.036e-5 | 7.326e-5 | 1.349e-6 |                     |

| 5v                            | 9.019e-4 | 1.398e-4 | 1.066e-4 | 9.039e-5 | 7.115e-5 | 6.752e-5 | 8.635e-7 |                     |

| 10v                           | 7.960e-4 | 1.181e-4 | 9.026e-5 | 7.950e-5 | 6.748e-5 | 6.538e-5 |          |                     |

| 20v                           | 7.217e-4 | 9.414e5  | 7.949e-5 | 7.267e-5 | 6.537e-5 | 6.422e-5 |          |                     |

## 4. Conclusion

The SPICE simulation results of our model shows improvement in the saturation frequency, OFF resistance to ON resistance ratio and switching time. Other model suffer from above problems. This model provide high off resistance to on resistance ratio hence it has more immunity to noise and works over wide range of applied voltage and frequency. The simulation results shows that the memristor works well at low voltage and over wide range of frequencies. In this paper we calculated operating range of memristor and calculated switching times over wide range of operating voltage and frequencies.

## References

- L. O. Chua, "Memristor The Missing Circuit Element," IEEE Transactions on Circuit Theory, Vol. 18, No. 5, Pp. 507–519, 1971. https://doi.org/10.1109/TCT.1971.1083337.

- [2] L. O. Chua and S. M. Kang, "Memristive Devices and Systems," Proceedings of the IEEE, Vol. 64, No. 2, Pp. 209–223, 1976. https://doi.org/10.1109/PROC.1976.10092.

- [3] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing memristor found," Nature, vol. 453, pp. 80–83, 2008. https://doi.org/10.1038/nature06932.

- [4] Y. Pershin and M. Di Ventra, Spin Memristive Systems, 2008. Arxiv preprint. [Online]. Available: http://arxiv.org/pdf/0806.2151

- [5] Y. Pershin and M. Di Ventra, "Current–voltage characteristics of semiconductor/ferromagnet junctions in the spin-blockade regime," Phys. Rev. B, Condens. Matter, vol. 77, no. 7, p. 073301, Feb. 2008. https://doi.org/10.1103/PhysRevB.77.073301.

- [6] G. Snider, "Computing with hysteretic resistor crossbars," *Applied Physics A*, vol. 80, pp. 1165–1172, 2005

- [7] S. Liu, "A new concept for non-volatile memory: The electric pulse induced resistive change effect in colossal magnetoresistive thin films," in Proc. Non-Volatile Memory Technol. Symp., 2001, pp. 1–7.

- [8] Y. Pershin and M. Di Ventra, "Memory effects in complex materials and nanoscale systems," Advances in Physics, vol. 60, no. 2, pp. 145–227, 2011. https://doi.org/10.1080/00018732.2010.544961.

- [9] O. Kavehei, S. Al-Sarawi, K. R. Cho, N. Iannella, S. J. Kim, K. Eshraghian, and D. Abbott, "Memristor-based synaptic networks and logical operations using in-situ computing," in International Conference Series on Intelligent Sensors, Sensor Networks and Information Processing, ISSNIP, 2011. https://doi.org/10.1109/ISSNIP.2011.6146610.

- [10] U. Ruhrmair, C. Jaeger, M. Bator, M. Stutzmann, P. Lugli, and G. Csaba, "Applications of high-capacity crossbar memories in cryptography," IEEE Transactions on Nanotechnology, vol. 10, no. 3, pp. 489–498, 2011. <a href="https://doi.org/10.1109/TNANO.2010.2049367">https://doi.org/10.1109/TNANO.2010.2049367</a>.

- [11] G. Csaba and P. Lugli, "Read-out design rules for molecular crossbar architectures," IEEE Transactions on Nanotechnology, vol. 8,

- no. 3, pp. 369–374, 2009. https://doi.org/10.1109/TNANO.2008.2010343.

- [12] A. Bushmaker, C. Chang, V. Deshpande, M. Amer, M. Bockrath, and S. Cronin, "Memristive behavior observed in defected single-walled carbon nanotubes," IEEE Transactions on Nanotechnology, vol. 10, no. 3, pp. 582–586, 2011. https://doi.org/10.1109/TNANO.2010.2053717.

- [13] Y. Xia, Z. Chu, W. Hung, L.Wang, and X. Song, "An integrated optimization approach for nano-hybrid circuit cell mapping," IEEE Transactions on Nanotechnology, 2011.

- [14] Z. Yang, C. Ko, and S. Ramanathan, "Oxide electronics utilizing ultrafast metal-insulator transitions," Annual Review of Materials Research, vol. 41, pp. 337–367, 2011. https://doi.org/10.1146/annurev-matsci-062910-100347.

- [15] Y. N. Joglekar and S. J. Wolf, "The elusive memristor: Properties of basic electrical circuits," Eur. J. Phys., vol. 30, no. 4, pp. 661– 675, Jul. 2009. https://doi.org/10.1088/0143-0807/30/4/001.

- [16] Z. Biolek, D. Biolek, and V. Biolkova, "SPICE model of memristor with nonlinear dopant drift," Radioengineering, vol. 18, no. 2, pp.210–214, Jun. 2009.

- [17] D. Biolek, Z. Biolek, and V. Biolkova, "SPICE modeling of memristive, memcapacitive and meminductive systems," in Proc. Eur. Conf.Circuit Theory Design, Aug. 2009, pp. 249–252.

- [18] A. Rak and G. Cserey, "Macromodeling of the memristor in SPICE," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 29, no.4, pp. 632–636, Apr. 2010. https://doi.org/10.1109/TCAD.2010.2042900.

- [19] S. Benderli and T. A.Wey, "On SPICE macromodelling of TiO2 memristors," Electron. Lett., vol. 45, no. 7, pp. 377–379, Mar. 2009. https://doi.org/10.1049/el.2009.3511.

- [20] D. Batas and H. Fiedler, "A memristor SPICE implementation and a new approach for magnetic flux-controlled memristor modeling," IEEE Trans. Nanotechnol., vol. 10, no. 2, pp. 250–255, Mar. 2011. https://doi.org/10.1109/TNANO.2009.2038051.

- [21] T. Prodromakis, B. P. Peh, C. Papavassiliou, and C. Toumazou, "A versatile memristor model with nonlinear dopant kinetics," IEEE Trans. Electron Devices, vol. 58, no. 9, pp. 3099–3105, Sep. 2011. https://doi.org/10.1109/TED.2011.2158004.

- [22] C. Yakopcic, T. M. Taha, G. Subramanyam, R. E. Pino, and S. Rogers, "A memristor device model," IEEE Electron Device Lett., vol. 32, no. 10, pp. 1436–1438, Oct. 2011. https://doi.org/10.1109/LED.2011.2163292.

- [23] C. Yakopcic, T. M. Taha, G. Subramanyam, and R. E. Pino, "Generalized memristive device SPICE model and its application in circuit design," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 32, no. 8, pp. 1201–1214, Aug. 2013. https://doi.org/10.1109/TCAD.2013.2252057.

- [24] A. Ascoli, R. Tetzlaff, F. Corinto, and M. Gilli, "PSpice switch-based versatile memristor model," in Proc. IEEE Int. Symp. Circuits Syst., May 2013, pp. 205–208. https://doi.org/10.1109/ISCAS.2013.6571818.

- [25] F. Corinto and A. Ascoli, "A boundary condition-based approach to the modeling of memristor nanostructures," IEEE Trans. Circuits Syst.I, Reg. Papers, vol. 59, no. 11, pp. 2713–2726, Nov. 2012.

- [26] Y. V. Pershin and M. Di Ventra, "SPICE model of memristive devices with threshold," Radioengineering, vol. 22, no. 2, pp. 485–489, Jun. 2013.

- [27] Y. V. Pershin, S. La Fontaine, and M. Di Ventra, "Memristive model of amoeba learning," Phys. Rev. E, vol. 80, no. 2, p. 021926, Aug. 2009. https://doi.org/10.1103/PhysRevE.80.021926.

- [28] P. Sheridan, K.-H. Kim, S. Gaba, T. Chang, L. Chen, and W. Lu, "Device and SPICE modeling of RRAM devices," Nanoscale, vol. 3, no. 9, pp. 3833–3840, 2011. https://doi.org/10.1039/c1nr10557d.

- [29] X. Guan, S. Yu, and H.-S. P.Wong, "On the switching parameter variation of metal-oxide RRAM—Part I: Physical modeling and simulation methodology," IEEE Trans. Electron Devices, vol. 59, no. 4, pp. 1172–1182, Apr. 2012. https://doi.org/10.1109/TED.2012.2184545.