International Journal of Engineering & Technology, 7 (1.1) (2018) 84-87

### **International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# Ultra low power design approach of asynchronous delta sigma modulator

Anil Kumar Sahu<sup>1\*</sup>, Rashid Sheikh<sup>2</sup>, A. Surendar<sup>3</sup>

<sup>1</sup>Assistant Professor, Department of Electronics & Telecommunication Engineering,

Shri Shankaracharya Group of Institutions, Bhilai (C.G.), India.

<sup>2</sup>M.E. Student, Department of Electronics & Telecommunication Engineering,

Shri Shankaracharya Group of Institutions, Bhilai (C.G.), India.

<sup>3</sup>Assistant Professor, School of Electronics, Vignan's Foundation for Science, Technology & Research, Guntur, India.

\*Corresponding author E-mail: anilkumarsahu12@outlook.com

#### **Abstract**

Asynchronous Delta Sigma Modulator (ADSM) is assuming an extremely vital part in the majority of conveying device and information convertor and in this manner requires the exceptional consideration in outlining. The execution of the vast majority of the device having DSM as an essential segment is described by the execution of the DSM hardware. This paper introduces the audit of work performed in planning of Asynchronous Delta Sigma Modulator. Latest trends are about the utilization of ADSM for various applications. Contrasting the execution of various ADSM circuits, an execution paradigm is settled for ADSM plan. The execution criteria basically think about the Low working voltages, low power utilization, high SNDR and better focus recurrence. At that point a strategy is suggested that characterizes the High execution ADSM that influence joined utilization of various methods to like inverse operation and mass driven MOS for ultra low power outline and enhancing the execution of an Asynchronous Delta Sigma Modulator.

Keywords: Asynchronous Delta Sigma Modulator (ADSM), Ultra Low Power Design, Centre Frequency, PSD.

### 1. Introduction

In spite of the way that most electronic hardware utilized is computerized, there are as yet various applications, for example, remote correspondences, sensors, and information stockpiling, [1] that will remain simple. Simple to computerized converters (ADCs) connect the simple world and the advanced computational area; in this manner their execution is urgent.

The most vital execution parameters of ADCs are the quantity of yield bits and accomplished flag data transfer capacity. Sigmadelta modulators give medium data transfer capacity and high number of bits; hence[2], they are requested for the most part by sound applications. The inspected and coded motion by the modulator must be bolstered into a digital channel to dispense with high recurrence undesired signs caused by oversampling. Constant time sigma-delta modulators expend less power contrasted with discrete time modulators. The proposed innovation in computerized CMOS forms result the expansion of the execution in the inherent speed of the transistors, give benefits for simple CMOS usage to get high time determination in the circuit application[3].

In this manner high exactness CMOS simple circuit can be gotten by utilizing simple flag in time space circuits rather than the customary voltage area. One of the time area simple circuit usage is an obligation cycle tweak or offbeat delta-sigma ( $\Delta \Sigma$ ) modulator. Synchronous delta sigma modulator utilizes worldwide clock for synchronization and in this manner its multifaceted nature increments because of synchronization hardware. Additionally, it utilizes a timed quantizer that presents a mistake

in yield flag. Where as in offbeat delta sigma modulator, no worldwide synchronous timed is utilized in this way circuit unpredictability is lessened. Likewise absence of timed quantizer influence its yield blunder to free, however because of essence of hysteresis comparator in an outline there is dependably nearness of comparator engendering postpone that presents change in time of yield

For quite a while the term low voltage was essentially utilized for circuits working under 3V which was fundamentally low when contrasted with gadgets working at 5v. Later on working voltages were fundamentally lessened to 1.8v to 1.2 v with innovation downsize process[4-5]. Scalling down is dependably not a decent decision for bringing down working voltages as it takes an expansive incentive to move starting with one process then onto the next. Considering the market drift, a superior gadget is ordinarily tried for its working voltages, recurrence reactions and power utilization. Talking genuinely, working voltages and power utilization contribute more for any gadget[6-8]. To accomplish low working voltages and low power utilization diverse methods like subthreshold operation, mass driven MOS are being utilized. These strategies permit to work the gadgets at nearly low voltages with low power utilization.

Utilization of mass driven transistor and working it in frail reversal or sub threshold locale is useful for low voltage and low power circuits. However, there is still issue of lessened gmb/gm proportion in Nanometre CMOS innovation. This is basically because of less changed grouping of foundation doping in various CMOS process. To set the lower limit voltages, corona embed method is utilized. How ever it is accounted for that utilization of radiance embed to battle short channel impacts has bizarrely

brought about extensive deplete actuated voltage move and bringing down yield impedance The related work about the past research is clarified in next areas.

## 2. Overview of different algorithms & related work

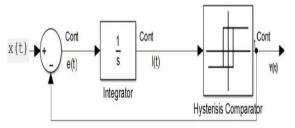

Fig.2 shows the architecture for ADSM proposed by Roza which is delta sigma modulator is completed and little of it concentrates on plan of low power and low working voltage outline. It is discovered that all the work concerning the low power have actualized mass driven MOSFET in frail reversal mode. Because of vast scaling in CMOS process short channel length impact have been happened, and distinctive diverting systems have been accounted for to moderate this impact. One of these method is utilization of radiance embed or stash embed.

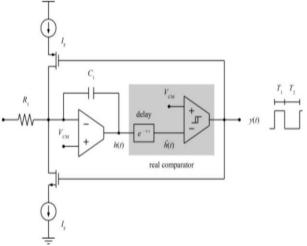

Outline of the low power ADSM is based on integrator and hysteresis comparator, where OTA is being a principle building square of integrator such a significant number of the scientists give weight on planning the OTA as general recurrence response of circuit is chiefly dependant on recurrence response of OTA. ADSM is broadly utilized as a part of correspondence framework for A/D transformation and prerequisite of A/D change shifts from application to application, along these lines noteworthy changes were seen in the ADSM circuits. In[7], an ADSM is intended for biomedical and sensor application working with vitality collected from condition. For this an ADSM working at 0.25v at low power is composed in it. Fig.1 demonstrates design for this work. To empower such a low voltage operation it utilizes approaches that incorporate mass driven MOSFET worked in powerless reversal district. At the point when mass driven MOSFETs are worked in weak inversion mode area, transconductance is diminished, in this way a method have been proposed for enhancing trans conductance in the same. To lessen the working voltages at exhibit innovation, change in doping fixation is of awesome significance. Radiance embed or take embed recommended for this reason. Utilization of corona embed have disadvantage of lessened yield protection.

Figure 1: Proposed block diagram of ASDM

Figure 2: Conventional block diagram of ASDM

ADSM designed in this is based on Roza's architecture which forms the close loop system with the integrator and hysteresis comparator. Integrator implemented is typically a first order integrator that makes use of enhanced Millar OTA. Work done in this gives the operating voltage of 0.25V with modulator centre frequency of 630 Hz. Also, it provides SNR of 62 Db which is quite low and has the scope of improvement. A very interesting and a big achievement made in this is a power consumption. This design typically consumes a very low power of 28 Nw which truly a low power design. In[8], DSM is reported as a duty cycle modulation. For this work DSM is used to perform the Analog to Digital conversion. DSM is widely used for D/A convertors by many researchers as it provides possibility of overcoming resolution problem in low voltage CMOS analog to digital convertors. Work performed here shows the very basic and detailed design for DSM. Still, many factors are remained to be address which are necessary for circuits in deep submicron region. Design proposed in this scheme is typically a Analog-to-Digital convertor that makes use of Asynchronous Delta Sigma Modulator whose design is appreciable. ADSM given in this literature is designed for a high band width requirement systems typically like a DSL. But due to synchronous operation, circuit complexity of this architecture is high. This DSM design typically operates at 1.8V and consumes 1.8mW of power. Design is implemented by using the second order integrator that leads it to more power consumption but with the benefit of better SNR of 70 dB and higher centre frequency. This work mainly focuses on Time-to-Digital- Convertor (TDC) and improvement in TDC for lossless reconstruction of information rather than focusing on DSM, but DSM implemented is of better performance and thus we found interest in it. In[10], comparison of different analog to digital conversion is performed. Detailed comparison of different A/D convertor schemes mainly Nyquist limit based ADC and oversampling based ADC. When Nyquist rate based ADC are considered, they extensively use clocked quantizer thus quantizer noise is always present at the output. When oversampled ADC is considered, instead of using quantizer it uses hysteresis comparator and whatever the noise generated is spread over the wide frequency range in the output and thus oversampled ADCs are also referred as noise shaping ADCs. Furthermore as operating voltages are reducing, this creates problem in output resolution in time domain. On the other hand, in oversampled ADC mainly in ADSM based ADC analog input is converted into continuous time but discrete amplitude output signal.

That means, amplitude axis is replaced by time axis, and due to availability of very fast CMOS devices we have good resolution over time axis[9]. In ADSM, hysteresis comparator is basic building block and centre frequency of ADSM completely depends on the hysteresis comparator propagation delay. Propagation delay is the time for which integrator integrates input signal and the integrator output overcomes the hysteresis level. If this propagation delay is large then centre frequency is small and ADSM performance degrades. If this overshoot remains in system then it will spread the period of output [3]. Thus propagation delay must be kept as low as possible for improved centre frequency. Based on the study of different Asynchronous Delta Sigma Modulator presented in [7][9][10] [11][12]with different application following comparison is carried out. A suitable design will be develop with the advantageous sets of design of different architectures.

### 3. Results and discussion

### **Transistor-level simulation**

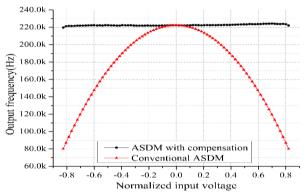

The comparison between the proposed ASDM and conventional one is shown in Fig. 3. The limit cycle frequency both proposed and conventional ASDM is set to be higher than 200kHz

(maximum 224kHz). When the maximum signal amplitude is applied, the output instantaneous frequency of the conventional ASDM drops to 80kHz. While for the proposed one, the output instantaneous frequency maintains to be over 200kHz over the entire input range.

Figure 3: Comparison of the output instantaneous frequency between the conventional ASDM and the proposed one

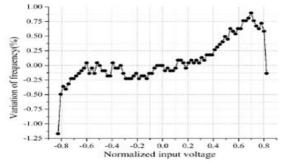

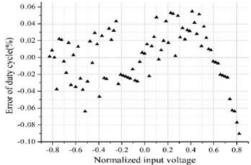

The stability of the output frequency is shown in Fig. 4. For the full range normalized input, the variation of the frequency is within 1.2%. While for the normalized input range from -0.4 to 0.4, the variation is within 0.25%. In that case, the proposed ASDM can be considered as an ideal pulse width modulator (PWM). The linearity of the proposed ASDM is shown in Fig. 5. Clearly the normalized error of the duty cycle is within 0.1% for the full range input.

Figure 4: Stability analysis of ASDM between normal input voltage and variation of frequency

Figure 5: Normalized error of the duty cycle of ASDM

In Fig.6 the PSD of the proposed ASDM is shown. Compared with Fig. 5, with the benefit of the frequency compensation, the number of limit cycle spectral components is reduced, and they are much further away from signal baseband. Therefore, the requirement of the limit cycle frequency of the proposed ASDM is reduced. In other words, the signal bandwidth of the proposed ASDM can be at least doubled with the same limit cycle frequency. The SFDR of the proposed modulator is over 72.4dB with signal bandwidth of 6kHz.

Figure 6: PSD of ASDM

### 4. Conclusion

Along these lines, here various ADSM designs are talked about which are predominantly worried about specific application. Taking a gander at the great sides of various application, a summed up design can be created with consolidating the great consequences of all engineering appropriately. In light of this, a framework will be produced that will work at 0.25V and with the base conceivable power utilization. A framework will likewise attempt to limit the spread deferral of hysteresis comparator so focus recurrence can be reasonably kept high that permits the utilization of design for extensive variety of uses.

We have demonstrated to execute an Asynchronous delta-sigma converter for simple to computerized change. The schmitt trigger displayed here is a totally original thought. To the best of our insight, this usage is the principal offbeat delta-sigma converter chip to have been effectively worked for simple to advanced transformation. We trust this engineering has guarantee for low power utilization in light of the extraordinary effortlessness of the required simple hardware and no requirement for high oversampling. The circuit configuration can be enhanced to bring down power prerequisites and increment usable info straight area for AC flag. The general ADC execution is controlled by the air conditioner curacy of the specimen time and will exploit the quicker hardware gave by the VLSI procedure scaling. Since the nonuniform specimen grouping is discrete in adequacy and strong to transmission commotion, the example succession can be transmitted out of the converter front end and the remaking calculation can be run remotely in areas where power and circuit measure are not a major issue. These attributes confirm that the nonconcurrent delta-sigma converter will probably be reasonable for control restricted applications, for example, remote detecting and embedded biomedical gadgets.

### References

- [1] Roza E, "Analog-to-digital conversion via duty-cycle modulation", IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process, Vol.44, No.11, (1997), pp.907–914.

- [2] Daniels J, Dehaene W, Steyaert MSJ & Wiesbauer A, "A/D conversion using asynchronous delta–sigma modulation and time-to-digital conversion", *IEEE Trans. Circuits Syst. I, Reg. Papers*, Vol.57, No.9, (2010), pp.2404–2412.

- [3] Matic T, Svedek T & Herceg M, "A method for the Schmitt-trigger propagation-delay compensation in asynchronous sigma-delta modulator", IEEE Transactions on Circuits and Systems II: Express Briefs, Vol.59, No.7, (2012), pp.404-408.

- [4] Ferreira LH & Sonkusale SR, "A 60-dB gain OTA operating at 0.25-V power supply in 130-nm digital CMOS process", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol.61, No.6, (2014), pp.1609-1617.

- [5] Manju, K., Sabeenian, R.S., Surendar, A."A review on optic disc and cup segmentation", (2017) Biomedical and Pharmacology Journal, 10 (1), pp. 373-379.

- [6] Surendar, A., Rani, N.U."High speed data searching algorithms for DNA searching", (2016) International Journal of Pharma and Bio Sciences, 2016 (Special Issue), pp. 73-77.

- Surendar, A., Arun, M."Efficient DNA sequence analysis for reduced gene selection using frequency analysis", (2016) Journal of

- Chemical and Pharmaceutical Sciences, 9 (4), pp. 3367-3373.

- [8] Surendar, A., George, A."A real-time searching and sequencing assembly platform based on an FPGA implementation for Bioinformatics applications", (2016) International Journal of Pharma and Bio Sciences, 7 (4), pp. B642-B647.

- [9] Daniels J, Dehaene W, Steyaert MS & Wiesbauer A, "A/D conversion using asynchronous delta-sigma modulation and time-to-digital conversion", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol.57, No.9, (2010), pp.2404-2412.

- [10] Chakraborty S, Mallik A, Sarkar CK & Rao VR, "Impact of halo doping on the subthreshold performance of deep submicrometer CMOS devices and circuits for ultralow power analog/mixedsignal applications", *IEEE Trans. Electron Devices*, Vol.54, No.2, (2007), pp.241–248.

- [11] Aziz PM, Sorensen HV & Vn der Spiegel J, "An overview of sigma-delta converters", *IEEE signal processing magazine*, Vol.13, No.1, (1996), pp.61-84.

- [12] Ouzounov S, Roza E, Hegt H, van der Weide G & van Roermund A, "An 8MHz, 72 Db SFDR Asynchronous Sigma-Delta Modulator with 1.5mW Power Dissipation", Symposium On VLSI Circuits Digest of Technical Papers, (2004).