International Journal of Engineering & Technology, 7 (2.25) (2018) 160-166

# **International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

# Space Vector Pulse Width Modulation Method to Reducing a Switching Loss in Inverter

S.M.Revathi<sup>1</sup>, C.R.Balamurugan<sup>2</sup>, N.Shanmugasundaram<sup>3</sup>

<sup>1</sup>Research scholar, Anna University, Chennai <sup>2</sup>Department of EEE, Karpagam College of Engineering, Coimbatore <sup>3</sup>Department of EEE, Vels Institute of Science Technology and Advanced Studies, Chennai, India \*Corresponding author Email: <sup>1</sup> seenurevas@gmail.com

#### **Abstract**

In This paper proposed an area space vector PWM technique that reduces switch victims of an electrical converter mainly efficiently by two-phase modulation technique. This technique chooses the most favorable one that minimizes a replacement switch (SW) defeat judgment supported lessening belongings in switch period allowing for section currents in numerous lessening patterns. This paper proposes an basic curved PWM technique. The planned technique created it attainable to scale back range of switch of the biggest or second major present section. And it will mechanically acclimatize to weight circumstances with varied power factors. Calculated switch wounded area unit condensed to regarding 50% by the planned technique.

Keywords: PWM, SVPWM, SW pattern.

## 1. Introduction:

The inverters area unit accustomed with controlled voltage and frequency convert the DC voltage into ac voltage. The wave shape of the final voltage depends on the switch states. Several applications of inverter face 3 major necessities. The harmonic contains the switching rate, and therefore the best utility. Drive devices unit higher than that with lofty harmonic contents. Towering switch frequency typically improves the standard of the motor currents and total performance of the drive devices. High switch frequency results in a lot of switch losses within the electrical converter switches. Conjointly high switch frequency is restricted by the switch capability of the switches. The simplest consumption of the DC voltage depends on the applied technique of switch. There area unit many schemes of switch the electrical converter switches similar to the six step electrical converter, physical phenomenon current controller, curved pulse breadth modulation, and house vector pulse breadth modulation. Every technique has its own benefits and drawbacks. Importance of **SVPWM** technique results in recent utilization of parallel 3 section Inverters mistreatment SVPWM technique.

Multilevel inverter generates sine voltages from discrete levels, and PWM scheme achieve this task of generating sinusoids of alternating voltage and frequency. SVPWM is taken into account a technique of PWM implementation, because it provides the subsequent benefits, (i) higher basic output voltage. (ii) Helpful in up harmonic presentation and reducing THD.(iii)Extreme simplicity and its straight forward and straight hardware accomplishment during a

Digital Signal Processor (DSP). (iv) SVPWM are often with efficiency dead during a few microseconds.

technique is commonly used for Sinusoidal PWM applications for dominant the electrical converter. During this pulse modulation technique is project enforced area and it's compared with curving pulse width technique visible of voltage utilization and total harmonic distortion. SPVWM technique is a lot of fashionable in currently compared with traditional schemes owing to its glorious options adore a lot of economical use of DC provide voltage, a lot of final voltage than typical modulation and forestall needless switch thus less commutation fatalities. The targets of SPVWM technique reference the voltage vector victimization the 8 switch patterns. Within the implementation of SPVWM, determination of reference voltage, switch time period, and switch time of every switch, are very important steps and switch sequence ought be such it offers less switch losses. A various operating intervals of the proposed converter were presented and charging mode to charge the battery the current flows through diode Dsn, meanwhile voltage stress on switch S4is decreased, leading to better efficiency. This paper contributes the energy stored in leakage-inductor is used for charging the battery and the proposed converter control strategies is applicable for power distribution by two input sources [21].

#### 2. Pulse Width Modulation:

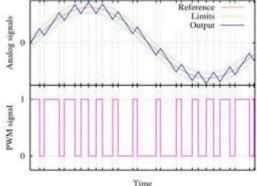

Pulse modulation consists in essence of sampling analog signals and then those samples area converted in to discrete pulses. The pulses are then transported from a sender to a receiver over a corporal broadcast means. PWM is termed as Pulse Duration Modulation(PDM) or Pulse Length Modulation(PLM). The width of the carrier pulses various in proportion with the amplitude of the modulating signal. In PWM noise is reduced because here amplitude is constant. No synchronization between transmitter and receiver.PWM technique is easy to separate the signal from noise.

Fig 1: Pulse Width modulation

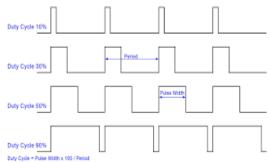

Fig 2: Duty cycle representation of PWM

#### 2.1. Fall in Figure of Switching Times:

#### 2.1.1 The concept of space vector P:

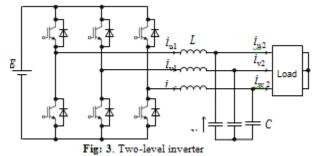

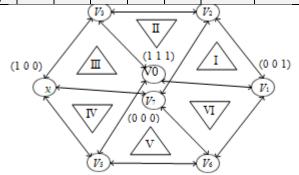

Three-phase PWM electrical converter control of manner in Fig.3 consists of half-dozen revolutionize modes (SM) in Fig.4 in keeping with final phases. Eight change vectors (SVs) from V7 V0 in Fig.5.in keeping with the standard PWM ways together with the triangular wave comparison methodology, one change cycle consists of 4 SVs. The 2-phase modulation methodology is as a result of its one change cycle consists of determined solely 3 SVs that square measure two vertex vectors of V0 or V7 and it will scale back variety of change times with efficiency. But variety of change times depends on a selected SP. once a SP of V0, V2, V3 is chosen, 2 switching's of phases u and v from V0 to V2, one change of section u from V2 to V3, and one change of section v from V3 to V0, altogether four switching's, square measure. Once a SP of V0, V3, V2 and another SP of V2, V3, V0 for come back is chosen, solely 2 change's square measure necessary for one switching cycle.

Fig: 3. Two-level inverter

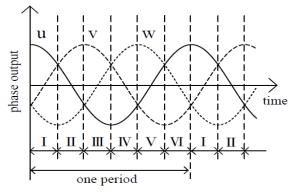

Fig 4:. Three-phase sinusoidal waveforms

**Table 1.** Distance between switch vectors

| S<br>V | V0      | V1      | V2      | V3      | V4      | V5      | V6      | V7     |

|--------|---------|---------|---------|---------|---------|---------|---------|--------|

| V<br>0 | -       | U       | UV      | V       | VW      | W       | WU      | UVW    |

| V<br>1 | U       | -       | V       | UV      | UV<br>W | WU      | W       | V<br>W |

| V<br>2 | UV      | V       | -       | U       | WU      | UV<br>W | VW      | W      |

| V<br>3 | V       | UV      | U       | -       | W       | VW      | UV<br>W | W<br>U |

| V<br>4 | VW      | UV<br>W | WU      | W       | -       | V       | UV      | U      |

| V<br>5 | W       | WU      | UV<br>W | VW      | V       | -       | U       | U<br>V |

| V<br>6 | WU      | W       | VW      | UV<br>W | UV      | U       | -       | V      |

| V<br>7 | UV<br>W | VW      | W       | UW      | U       | UV      | V       | -      |

Fig 5. Rule between various switch vectors.

Shift of 2 phases u and v are required for transmitting from V1 to V3 & this respond to ultraviolet. At hand aren't any shifts

between constant SV & this respond to"-" within the diagonals. A minimum of one shift is required for several evolution. There are twelve transition mentioned u, v, w within the table that consider avoiding inessential shift. The twelve transition are shown by the arrows in Fig.5.

As in Fig.5, a position SV in SM I is generate because of the four SPs are V0, V1, V2, V2, V1, V0, V7, V2, V1, and V1, V2, V7 with the bare smallest amount two switching's. One SP which one is identical to last SP of the preceding switch cycle should selected. The condition is that the same for the opposite SM and variety of the switch is 2 that is condensed to two/three times of the traditional switch.

Once there's a SM amendment, true desires a bit modification. May be, for a form evolution from SM I to a different. A SP whose beginning SV is that the same because SP is chosen to keep away from unessential transportation switch. May be, the transition from SM I of V0, V1, V2 to SM II selects V2, V3, V0 to keep happy the continual circumstance. SM desires associate degree transitional nothing SV. These rules minimize variety of switching.

#### 2.1.2. PWM Duty-Ratio fortitude:

Fortitude, initial duties uu, uv, uw of the 3-phases are calculated from the three final voltages consistent with a reference vector wherever uu, uv, uw are outlined to satisfy the subsequent balance equation.

$$uu + uv + uw = 0 \tag{1}$$

They are converted to ua, ub, uc for selected three SVs Va, Vb, Vc. The relative sandwiched between the orientation and therefore the house vectors  $V\alpha$ ,  $V\beta$  in SM I is described in Fig.4. The orientation in one in every of the opposite SMs is regenerate to SM I by Associate in attention of applicable rotary motion process. The orientation mechanism, ux and uy, are calculated from uu, uv, uw as follows.

$$\begin{bmatrix} u_x \\ u_y \end{bmatrix} = \frac{1}{2} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} u_u \\ u_v \\ u_w \end{bmatrix}$$

(2)

According to Fig.4,  $u\alpha$ ,  $u\beta$ , uz are calculated from ux and uy.

### 3. Principle of SVPWM:

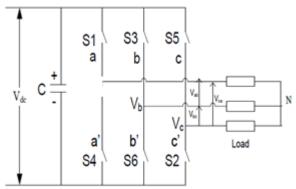

Initially, a three-phase electrical converter is bestowed on the idea of area illustration. S1 to S6 are the 6 switches that form the final, that are forbidden by the change variables a, a', b, b', c and c'. Once a higher semiconductor unit is switched on. The states of the higher switches S1, S3, S5 will be wont to confirm the final voltage.

Fig.6: Power circuit of a 3phase VSI

The connection flanked by switch changeable vector [a, b, c] and row-to-row voltage vector [Vab Vbc Vca] is written as,

$$\begin{bmatrix} V_{ab} \\ V_{bc} \\ V_{ca} \end{bmatrix} = V_{dc} \begin{bmatrix} 1 & -1 & 0 \\ 0 & 1 & -1 \\ -1 & 0 & 1 \end{bmatrix} \begin{bmatrix} a \\ b \\ c \end{bmatrix}$$

As illustrate in Fig. 6, area unit potential combos of on and off patterns for the 3 higher authority switches. The ON and OFF states area unit conflicting to the higher one so area unit simply strongminded after the states of the higher power transistors area unit strong-minded.

The eight change vectors, final streak to impartial voltage, and final streak-to-streak voltages in terms of DC-link VDC and Fig.6 eight electrical converter.

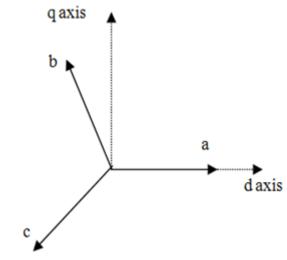

Fig 7: The relationship of a b c reference frame and stationary d-q reference frame

Table 2: Switching vectors.

| Tuble 21 8 Witching Vectors. |                      |   |   |                         |      |      |                      |     |     |

|------------------------------|----------------------|---|---|-------------------------|------|------|----------------------|-----|-----|

| Voltage<br>Vectors           | Switching<br>Vectors |   |   | Line to neutral voltage |      |      | Line to line voltage |     |     |

| vectors                      | a                    | b | С | Van                     | Vbn  | Vcn  | Vab                  | Vbc | Vca |

| V0                           | 0                    | 0 | 0 | 0                       | 0    | 0    | 0                    | 0   | 0   |

| V1                           | 1                    | 0 | 0 | 2/3                     | -1/3 | -1/3 | 1                    | 0   | -1  |

| V2                           | 1                    | 1 | 0 | 1/3                     | 1/3  | -2/3 | 0                    | 1   | -1  |

| V3                           | 0                    | 1 | 0 | -1/3                    | 2/3  | -1/3 | -1                   | 1   | 0   |

| V4                           | 0                    | 1 | 1 | -2/3                    | 1/3  | 1/3  | -1                   | 0   | 1   |

| V5                           | 0                    | 0 | 1 | -1/3                    | -1/3 | 2/3  | 0                    | -1  | 1   |

| V6                           | 1                    | 0 | 1 | 1/3                     | 1/3  | 1/3  | 1                    | -1  | 0   |

| V7                           | 1                    | 1 | 1 | 0                       | 0    | 0    | 0                    | 0   | 0   |

To implement SVPWM, the equations in voltage within the fundamentals system may be reworked into the stationary dq system that consists of the horizontal (d) and vertical (q) axes as delineate in Fig7.

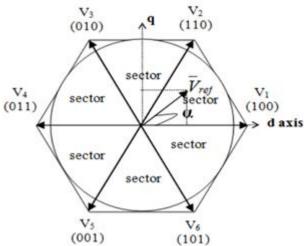

Fig 8: Eight inverter voltages vectors (V0 to V7)

This alteration is corresponding to associate degree orthogonal outcrop of [a, b, c] onto the two-dimensional at right angles to the vector [1, 1, 1] in a very three-dimensional coordinate devices. Six non-zero (active) vectors and 2 zero vectors are doable as a final result.

Six (V1 V6) form the polygonal non-zero vectors shape as portrayed in Fig.9, and feed power to the devices. The eight vectors are known as the fundamental area vectors and are denoted by V0(000), V1(100), V2(110), V3(010), V4(011), V5(001), V6(101), V7(111). The binary numbers indicate the switch state of electrical converter legs Identical transformation is applied to the specified final voltage to induce the specified reference voltage vector V<sub>ref</sub> within the d-q plane. One easy technique of approximation is to get the common final of the electrical converter in an exceedingly little amount, T to be identical as that of V<sub>ref</sub> within the same amount. SVPWM refers to a special switch sequence of the higher power switches of a three-phase power electrical converter.

Fig.9:Basic switching vectors and sectors

#### 4. Proposed Method

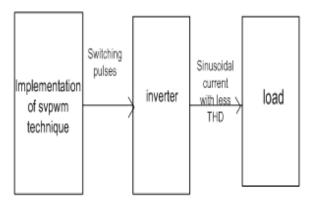

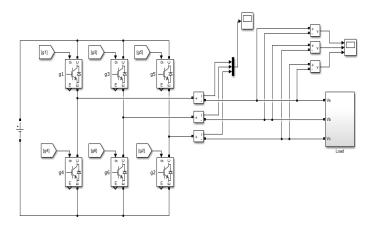

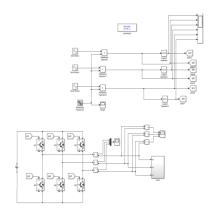

Fig.10: Block diagram of control method

Fig. 10 shows the block diagram for proposed method. In this control method switching pulses required for the inverter to produce sinusoidal current are generated by SVPWM scheme. The control method is developed totally in the matlab environment using matlab Simulink [7-9]. This control method can also implement using mat lab coding. SVPWM scheme is applied for three phase two level inverter, and it is applied for both Balanced and Unbalanced loads. This method gives better DC bus utilize and less total harmonic distortion when compared to sinusoidal pulse width modulation.

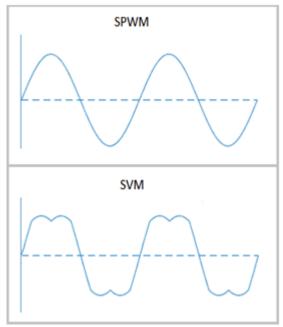

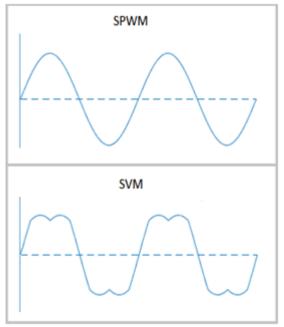

# 5. Evaluation of Sinusoidal PWM and Space Vector PWM:

- 1) Within the Fig. 12 above, U1 is that the curved reference voltage. However the triple order harmonics aren't appeared within the stage-to-stage voltage yet. This may ends up in the upper modulation directory while comparing with that to the SPWM.

- 2) SPWM solely reaches to seventy eight percentage of square-wave process, however the amplitude of most doable voltage is ninety percentage of square-wave within the area vector PWM.

Fig.11: signal comparison for SPWM and SVM.

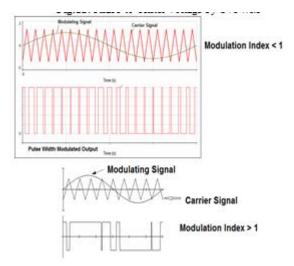

### 6. Modulation Index:

When the modulation index m reaches 1.0,the under modulation region soak at 78%. As the modulating wave exceed the max out of the carrier wave ,PWM over modulation (m>1.0).

Fig.12: Phase-to-center voltage by SVPWM

Fig.13: PWM Modulation index

Table 3: Effects of modulation index on THD of the PWM Scheme.

| ma   | %THD | ma   | %THD |

|------|------|------|------|

| 0.3  | 7.45 | 0.75 | 3.12 |

| 0.4  | 9.74 | 0.8  | 3.42 |

| 0.5  | 5.13 | 0.85 | 2.58 |

| 0.55 | 5.24 | 0.9  | 2.08 |

| 0.6  | 6.03 | 0.95 | 2.20 |

| 0.65 | 3.74 | 1    | 2.81 |

| 0.7  | 3.37 |      | ·    |

# 7. Matlab Simulations:

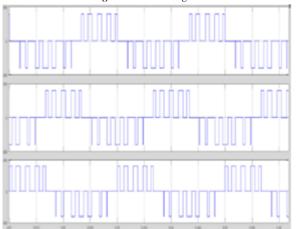

Fig.14: simulation model of SPWM

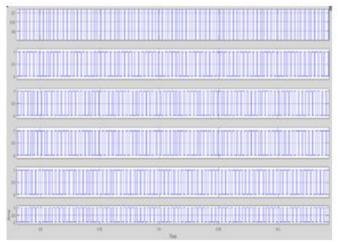

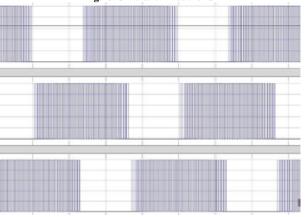

Fig.15: SPWM voltage waveform

Fig.16: SPWM current waveform.

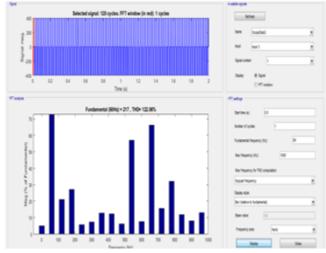

Fig.17: SPWM THD%

Fig.18: Simulation model of SVPWM

Fig.19:SVPWM voltage waveform

Fig.20: SVPWM current waveform.

Fig.21: SVPWM THD%

#### 8. Conclusion:

In this manuscript, a bearing method for the converter victimization SVPWM is projected. The projected management technique is finished in MATLAB Simulink tool. The vocal band below nonlinear pack circumstances describes that lessening of band is healthier. The simulation learning of two level converter is administrated victimization SVPWM as a result of its higher operation of DC bus voltage extra professionally and develop a amount of vocal deformation in three-phase voltage provide converter. This result (harmonic spectra) explains SVPWM management for two-level inverters has become in style. Within the vary of linear-modulation, not solely sleek management over the elemental element of the final voltage is obtained, however additionally the harmonic spectrum is appropriate. By increasing the change frequency, one might push important harmonics more up. For prime power applications additionally this can be used for reducing change losses within the power semiconductor devices.

#### References

- K. Taniguchi, H. Irie; "Trapezoidal modulating signal for three-phase pwm inverter," IEEE Transactions on Industrial Electronics, Vol. 33, No.2, 193 - 200, 1986.

- [2] S. Halasz, B.T. Huu, A. Zakharov; "Two-phase modulation technique for three-level inverter-fed AC drives," IEEE Transactions on Industrial Electronics, Vol. 47, No.6, pp.1200 - 1211, 2000.

- [3] M.C. Cavalcanti, E.R.C. da Silva, A.M.N Lima, C.B. Jacobina, R.N.C.Alves; "Reducing losses in three-phase PWM pulsed DC-link voltage type inverter devicess," IEEE Transactions on Industry Applications, Vol.38, No.4, pp. 1114 - 1122, 2002.

- [4] Hideaki Fujita, Ryo Suzuki: "A three-phase solar power conditioner

- [7] J. I. León, O. López, L. G. Franquelo, J. Doval-Gandoy, S. Vázquez, J. Alvarez, and F. D. Freijedo, "Multilevel multiphase feedforward space vector modulation technique," IEEE Trans. Ind. Electron., vol. 57, no. 6, pp. 2026–2075, Jun. 2010.

- [8] A. M. Hava and E. U<sup>\*</sup> n, "Performance analysis of reduced common mode voltage PWM methods and comparison with standard PWM methods for three-phase voltage source inverters," IEEE Trans. Power Electron., vol. 24, no. 1, pp. 241–252, Jan. 2009.

- [9] Aneesh Mohamed A. S., Anish Gopinath, and M. R. Baiju, Member, IEEE, "A Simple Space Vector PWM Generation Scheme for Any General n-Level Inverter", IEEE Transactions on industrial electronics, vol. 56, no. 5, pp. 16-49, may 2009.

- [10] R.H. Zhang, H.T.Wu, C. Du, L.R Zhang, "Hysteresis Space Vector Control for Parallel Active Power Filter", IEEE, 2009

- [11] V. S. S. Pavan Kumar Hari and G. Narayanan, "Comparative evaluation of space vector based pulse width modulation techniques in terms of harmonic distortion and switching losses," in Proc. MCDES, May 2008.

- [12] Z. Shu, J. Tang, Y. Guo, and J. Lian, "An efficient SVPWM algorithm with low computational overhead for three-phase inverters," IEEE Trans. Power Electron., vol. 22, no. 5, pp. 1797–1805, Sep. 2007.

- [13] Zhang Qing, Zhang Chun-X, "Study on SVPWM Technique of Three-phase voltage Source Rectifier", Journal of Heilongjiang Hydraulic EngineeringCollege, Vol.33(1), pp.38-40, Mar. 2006.

- [14] Dan.S.G, Benjamin.D.D, Magureanu.R, Asimionoaei.L, Teodorescu.R, Blaabjerg.F, "Control strategies of active filters in the context of power conditioning," IEEE Trans. on Ind. applications, vol.25,11-14, pp.10-20, Sept-2005.

- [15] Rathnakumar.D,LakshmanaPerumal,Srinivasan.T, "A new software implementation of space vector pwm," IEEE Trans. Power Electron., vol.14, pp.131-136,8-10 April 2005.

- [16] C.R.Balamurugan, "Three Area Power System Load Frequency Control Using Fuzzy Logic Controller" International Journal of Applied Power Engineering, ISSN No. 2252-8792, vol.7, no.1, pp. 18-26, April 2018.

- [17] C.R.Balamurugan, R.Bensraj, "Analysis of Various Carriers Overlapping PWM Strategies for a Single Phase Ternary Multilevel Inverter" International Journal of Applied Power Engineering, ISSN No. 2252-8792, vol.7, no.1, pp.27-39, April 2018.

- [18] R.Umamageswari, C.R.Balamurugan, T.A.Ragavendiran, "Selective Harmonics Mitigation Modulation Scheme Applied to CHB and NPC Multilevel Inverters", Journal of Electrical Engineering, ISSN No: 1582-4594, Vol. 18, No.2, pp. 1-8, June 2018.

- [19] C.R.Balamurugan, K. Vijayalakshmi, "Comparative Analysis of Various Z-source Based Five Level Cascaded H-bridge Multilevel Inverter" Bulletin of Electrical Engineering and Informatics, ISSN No. 2302-9285, vol.7, no.1, pp. 1-14, March 2018.

- [20] C.R.Balamurugan, A.N.Abhirami, "Z Source Fed H-Type Diode Clamped Multilevel Inverter", Journal of Advanced Research in Dynamical and Control Systems, ISSN 1943-023X, Special Issue: 17, Nov 2017, pp. 1785-1794.

- [21] S.Pradeep Kumar, R.Krishnakumar, E.N.Ganesh, "Multi-input Multi- output converter for battery charger with low power applications", International Journal of Engineering & Technology, Volume -7, Special Issue- (2.25) (2018) Page No:64-67.