International Journal of Engineering & Technology, 7 (2.8) (2018) 30-34

# **International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research Paper

# A 14-bit 10kS/s power efficient 65nm SAR ADC for cardiac implantable medical devices

Bala Dastagiri Nadhindla 1\*, K Hari Kishore 2

<sup>1</sup> Research Scholar, Koneru Lakshmaiah Education Foundation, Vadeeswaram, Guntur, A.P., India 522502

<sup>2</sup> Professor, Koneru Lakshmaiah Education Foundation, Vadeeswaram, Guntur A.P., India. 522502

\*Corresponding author E-mail: baluece414@gmail.com

#### **Abstract**

This brief presents a 10kS/s 14 bit 12.5 ENOB Successive Approximation Register Analog-to- Digital Converter for Cardiac Implantable Medical. For achieving power efficient operation, SAR ADC employ SAR control, a new power and noise efficient comparator topology, non- binary weighted capacitive DAC. The linearity of implemented SAR ADC is enhanced with the uniform geometry of non-binary weighted capacitive DAC. The proposed SAR ADC is implemented using 65nm CMOS technology. The latched comparator consumes a power of 2.4uW and it provides an ENOB of 12.6 at a supply voltage of 1V.The INL is between -2.7/+1.6 LSB and DNL is between -0.6/+1.4LSB. The FOM of ADC is 40fJ/conv. Step which is comparable with existing ADC topologies.

Keywords: Successive Approximation Register Analog-to-Digital Converter; ENOB; INL; DNL; Cardiac Implantable Medical Device; Comparator.

#### 1. Introduction

The advancement in CMOS Technology has spurred increasing demand for integrated cardiac implantable medical devices like defibrillators and pacemakers. These implantable devices have to operate with a non-rechargeable battery over their life time almost for 10 years. Among various components available in the implantable devices, Analog-to-Digital Converters are power hungry and also the most critical component in measuring cardiac signals. Cardiac Signals are low frequency analog signals and doesn't require high speed for their conversion. Thus designing an ADC for cardiac applications with low power consumption and required conversion accuracy makes it a great challenge. Successive Approximation ADCs are being widely used in biomedical applications as they operate with low speed and medium resolution and also with low power budget. Also the main reason for utilizing SAR ADCs in cardiac Implantable devices is due to their simplicity in their structure. Normally SAR ADCs show very high energy efficiency, but due to comparator noise and capacitor mismatch. SAR ADCs are limited to medium resolution. To overcome the effect of capacitor mismatch, binary weighted capacitance array in DACs has been implemented in [1], [2]. An alternative technique called dithering has been proposed to cancel the errors in the DAC and also to improve the linearity [3], [4]. Many attempts have been made to cut down the power consumed by SAR ADC with the prominence on designing latched comparator and capacitive DAC. In this work, Low power SAR ADC is designed by modifying the existing architectures of latched comparator and effective capacitive DAC. The architecture of DAC is modified such that the size of capacitance in the DAC is reduced and in turn power consumption and area of DAC are also reduced. In this work, the implementation of non-binary weighted DAC is done. This type of converter exhibits redundancy during the conversion but however array capacitance value in the DAC is rounded off to the nearest integer value, such that it leads to uniform geometry. Moreover,

the power consumption of latched comparator is also reduced by modifying its architecture, which indeed reduces the charge injection, kickback noise and clock feedthrough.

The organization of the brief is as follows. The architectural implementation of an ADC is discussed in section II. The simulation results of SAR ADC and its comparison is presented in section III followed by conclusion remarks in section IV.

# 2. Proposed architectural implementation of SAR-ADC

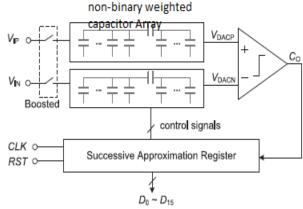

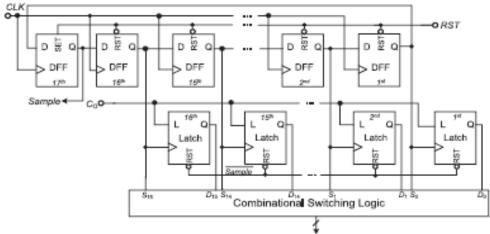

The architecture of SAR ADC implementing in cardiac IMDs is depicted in figure 1. It mainly consists of a synchronous SAR, latched dynamic comparator and a non-binary differential weighted capacitive DAC and. The differential inputs to the DAC are sampled on the capacitive array by using bootstrapped switches.

Fig. 1: Architecture of Proposed SAR ADC.

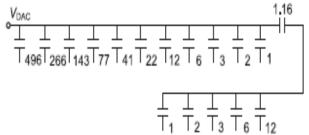

#### a) Capacitive DAC

In order to achieve a 14 bits resolution, we have implemented a split array DAC consisting of 11 bits primary DAC and a secondary DAC of 5 bits along side of bridge capacitor. For achieving uniform geometry and good linearity, the implemented value of non-binary capacitive array is adjusted to the nearby integer value. After adjusting the value, the dynamic range of capacitive DAC has to be greater than 14 bits resolution. The capacitor in the capacitance array is implemented such that its density is high. The value of each capacitance is approximately 27fF where as total capacitance of sampling capacitance is about 30pF. The non binary weighted capacitive array is shown in figure 2.

Fig. 2: Non-Binary Weighted Capacitance Array Rounded Off to Nearest Integer Value.

For a non –binary weighted capacitor array split DAC has radix k, the capacitors present at the bridge capacitor terminals also has the radix. Here primary plate of bridge capacitor is joined to secondary DAC, such that the linearity error occurred due to parasitic can be minimized. To enable the ADC for correcting under approximation and over approximation decision errors , it is required that the decision levels are shifted to middle of redundancy stage [6], [7]. For shifting the level, an additional capacitor is used besides the main capacitance array [5]. A new approach is introduced in which decision bit and lower weighted bit are switched simultaneously[8], [9]. Once the decision is happened, lower order bit is turn downed to its original state. The secondary bit has a weight equal

to the redundancy of decision bit. The position of Secondary bit is written as

$$W_j + \frac{1}{2} \cdot \left( \sum_{i=1}^{j-1} W_i - W_j \right) = W_j + W_{j-k}$$

Where k is denoted as distance between the decision and secondary bits and  $W_j$  is the weight of the decision bit [10].

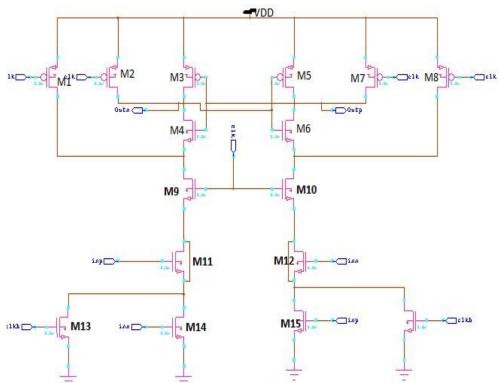

#### b) Latched Comparator

In a latched comparator, apart from thermal noise, clock feed-through ,comparator offset voltage, kickback noise; and charge injection are also the main sources of errors. In a SAR ADC, the offset in transfer curve can be corrected easily, therefore offset of the latched comparator can be easily tolerated. Moreover, the other sources of errors must be reduced. Using a few traditional techniques may reduce the errors but considerably increases power consumption [11], [12].

Kickback noise and clock feedthrough are produced at the edge of the latched comparator output signal and at the clock of the comparator respectively. In case of cardiac applications, the latched comparator has low clock frequency and hence the latched comparator has ample time for making its decisions. Therefore kickback noise and clock feedthrough can be reduced by increasing raise time and fall time of comparator clock and its output signal. The architecture of proposed comparator is depicted in the figure 3. When the latched comparator is reset state, both the outputs of the dynamic latched are pulled to VDD. As the transistors M9 and M10 are in OFF state, they isolate the inputs from being connected to output. During the comparison phase the outputs are pulled to VDD and GND depending on the inputs applied. If INP>INN, the corresponding output OUTP tends to discharge to ground faster than OUTN through the transistors M13 and M14. The transistors M11 and M12 are connected in a fashion such that the charge injection and clock feedthrough is reduced. Due to the isolation transistors M9 and M10 the outputs doesn't have any effect on the inputs of the comparator during the transition of the latch.

Fig. 3: Architecture of Proposed Latched Comparator to Minimize Kickback Noise and Clock Feedthrough.

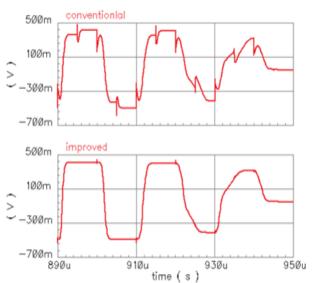

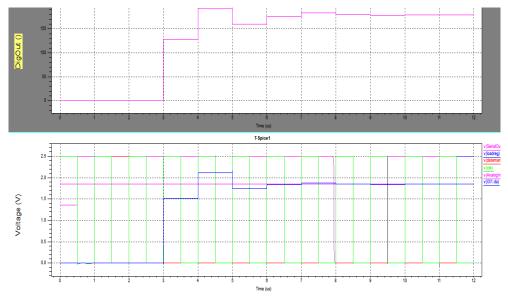

From the figure 4, it is seen that the conventional latched comparator suffers from more kickback noise(glitches can be seen) when compared with proposed architecture. In the proposed architecture, the common mode signal  $V_{\rm CM}$  is kept above the threshold voltage that is in between mid rail voltages.

Fig.4: Transient Simulation Results of Latch Input.

#### c) Sar Digital Control Logic

SAR logic control is demonstrated in figure 5.It mainly consists of positive transparent latches, shift registers and a combinational logic switch. The latch is used to store the decisions taken by the comparator, combinational logic switch is used to generate the control signals required for differential DAC and shift register is used to generate pulses. In this work, to complete a single conversion we require a 17 clock cycles, 16 for bit decisions and remaining for sampling [13], [14].

Fig. 5: Block Diagram of SAR Digital Control Logic.

#### 3. Experimental results

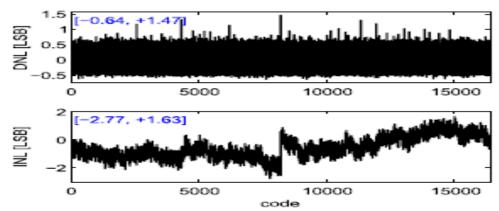

In this work, the SAR ADC is implemented using 65nm CMOS technology. Also the proposed 10KS/s SAR ADC is measured at a supply voltage of 1V.The transient simulation result of SAR ADC is plotted in the figure 6.The static performance of an ADC is measured and depicted in Figure 7.The peak Value of Differential Non Linearity error is +1.4/-0.6 LSB where as Peak value of Integrated Non Linearity error is +1.6/-2.7 LSB. The dynamic perfor-

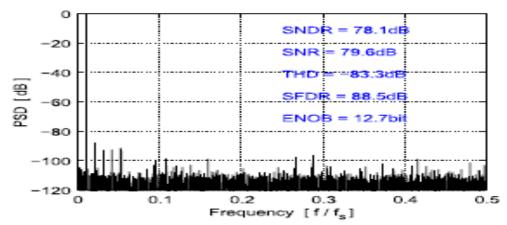

mance characteristics of SAR ADC is plotted in figure 8. The SNDR and SFDR are constant with a minimum value of 78db and 88db respectively providing 12.5 effective no.of bits(ENOB). The SAR ADC consumes a total power consumption of 2.4uW where latched comparator consumes 75% of power, DAC consumes 20% and SAR control logic consumes 5% of power. The important benchmarks of SAR ADC are defined as Figure-of-Merit (FOM) =Ptotal/(2ENOB \*fs), where ENOB, Ptotal and fs are Effective Number of Bits, Total Power consumption and Nyquist frequency.

Fig. 6: Transient Analysis of Proposed SAR ADC.

Fig. 7: Measurement of Static Performance of SAR ADC.

Fig. 8: Measurement of Dynamic Performance of SAR ADC.

Also the table I shows the comparison performance of proposed SAR ADC with other architectures.

Table 1: Performance Comparison In this work [4] [10] [2] Technology (um) 0.09 0.09 0.065 0.045 0.180 0.065 Resolution (bits) 13 14 14 14 18 14 Sampling rate(S/s) 51M 127K 82M 37M 6M 10K Supply voltage(v) 1.2 1.5 1.2 2.2 5 -0.6/+1.4LSB DNL INL -2.7/+1.6LSB SFDR(db) 84 87.1 80.3 90 88 SNDR(db) 69.1 79.1 71.3 74.4 78 3.9m 2.4uPower(w) 1.67u 32.2m 56.6m 32.82mENOB(bits) 11.6 13 11.8 12.1 12.6 FOM(fJ/conv. Step) 36 23 129 363 88 40

#### 4. Conclusion

In this work, a 14b 10kS/s SAR ADC has been implemented for cardiac IMDs in 65nm CMOS technology. To minimize power consumption, a new power and noise efficient latched comparator has been proposed. The proposed ADC achieves a power consumption of 2.4uW. It utilizes a non-binary weighted capacitive array whose value is rounded to nearer integer value. The uniform geometry of DAC helps to enhance the linearity of ADC. The INL is between -2.7/+1.6 LSB and DNL is between -0.6/+1.4LSB. The FOM of ADC is 40fJ/conv. Step which is comparable with existing ADC topologies.

## Acknowledgements

The authors would like to thank Annamacharya Institute of Technology and Sciences, Rajampet and K L University for the providing the required facilities to carry out the work.

### References

- TiHealthTech health guide, Texas Instruments, Dallas, TX, USA, 2013.

- [2] T. Morie et al.,: A 71 dB-SNDR 50 MS/s 4.2 mW CMOS SAR ADC by SNR enhancement techniques utilizing noise, in Proc. ISSCC Dig. Tech. Papers, Feb. 2013, pp. 272–273.

- [3] H. S. Lee, D. Hodges, and P. R. Gray : A self-calibrating 15 bit CMOS A/D converter, IEEE J. Solid-State Circuits, vol. 19, no. 6, pp. 813–819, Dec. 1984. https://doi.org/10.1109/JSSC.1984.1052231.

- [4] P. Harpe, E. Cantatore, and A. von Roermund: An oversampled 12/14b SAR ADC with noise reduction and linearity enhancements achieving up to 79.1 dB SNDR, in Proc. ISSCC Dig. Tech. Papers, Feb. 2014, pp. 194–195.

- [5] W. Liu, P. Huang, and Y. Chiu: A 12-bit, 45-MS/s, 3-mW redundant successive-approximation-register analog-to-digital converter with digital calibration, IEEE J. Solid-State Circuits, vol. 46, no. 11, pp. 2661–2672, Nov. 2011. https://doi.org/10.1109/JSSC.2011.2163556.

- [6] R. Kapusta et al.: A 14b 80 MS/s SAR ADC with 73.6 dB SNDR in 65 nm CMOS, in Proc. ISSCC Dig. Tech. Papers, Feb. 2013, pp. 472–473

- [7] D. Zhang and A. Alvandpour: Analysis and calibration of nonbinaryweighted capacitive DAC for high-resolution SAR ADCs, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 61, no. 9, pp. 666–670, Sep. 2014.

- [8] Z. Boyacigiller, B. Weir, and P. Bradshaw: An error-correcting 14b/20 μs CMOS A/D converter, in Proc. ISSCC Dig. Tech. Papers, Feb. 1981, pp. 62–63.

- [9] A. M. Krämer, E. Janssen, K. Doris, and B. Murmann,: A 14b 35 MS/s SAR ADC achieving 75 dB SNDR and 99 dB SFDR with loop-embedded input buffer in CMOS: in Proc. ISSCC Dig. Tech. Papers, Feb. 2015, pp. 284–285.

- [10] Bannon, C. P. Hurrell, D. Hummerston, and C. Lyden:An 18b 5 MS/s SAR ADC with 100.2 dB dynamic range: inProc. VLSI Symp., Jun. 2014, pp. 1–2.

- [11] B. Razavi: Design of Analog CMOS Integrated Circuits. NewYork,NY, USA: McGraw-Hill, 2001.

- [12] B. Murmann, ADC Performance Survey 1997–2015.

- [13] Zhangming Zhu, and Yuhua Liang,: A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC inv0.18um- CMOS for Medical Implant Devices, IEEE Journal of solid state circuits, Vol. 62, N0-9, and September 2015.

- [14] Dai Zhang, Ameya Bhide, Atila Alvandpour,:A 53-nW 9.1-ENOB 1-KS/s SAR ADC in 0.13um CMOS for Medical Implant Devices, IEEE Journal of solid state circuits, Vol. 47, N0-7, and July 2012

- [15] SHAIK.RAZIA, M.R.NARASINGARAO published "A Neuro computing frame work for thyroid disease diagnosis using machine learning techniques" in Scopus Indexed Journal JATIT (Journal of Theoretical and Applied Information Technology, 15th May 2017. Vol.95. No.9. Pages 1996-2005) ISSN: 1992-8645 www.jatit.org E-ISSN: 1817-3195.

- [16] SHAIK.RAZIA, M.R.NARASINGARAO published "Machine learning techniques for thyroid disease diagnosis - A review" in

- Scopus Indexed Journal INDJST (Indian Journal of Science and Technology, ISSN: 09746846, volume-9, Issue 28, July 2016, Article number 93705).

- [17] Dr. Seetaiah Kilaru, Hari Kishore K, Sravani T, Anvesh Chowdary L, Balaji T "Review and Analysis of Promising Technologies with Respect to fifth Generation Networks", 2014 First International Conference on Networks & Soft Computing, ISSN:978-1-4799-3486-7/14,pp.270-273,August2014.

- [18] Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- [19] P Bala Gopal, K Hari Kishore, B.Praveen Kittu "An FPGA Implementation of On Chip UART Testing with BIST Techniques", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34047-34051, August 2015.

- [20] Murali, K Hari Kishore, D Venkat Reddy "Integrating FPGAs with Trigger Circuitry Core System Insertions for Observability in Debugging Process" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.11, Issue No.12, page: 2643-2650, December 2016.

- [21] A. Mahesh Mudavath, K Hari Kishore, D Venkat Reddy "Design of CMOS RF Front-End of Low Noise Amplifier for LTE System Applications Integrating FPGAs" Asian Journal of Information Technology, ISSN No: 1682-3915, Vol No.15, Issue No.20, page: 4040-4047, December 2016.

- [22] N Bala Dastagiri, K Hari Kishore "Novel Design of Low Power Latch Comparator in 45nm for Cardiac Signal Monitoring", International Journal of Control Theory and Applications, ISSN No: 0974-5572, Vol No.9, Issue No.49, page: 117-123, May 2016.

- [23] N Bala Gopal, Kakarla Hari Kishore "Reduction of Kickback Noise in Latched Comparators for Cardiac IMDs" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.43, Page: 1-6, November 2016.

- [24] S Nazeer Hussain, K Hari Kishore "Computational Optimization of Placement and Routing using Genetic Algorithm" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.47, page: 1-4, December 2016.

- [25] N.Prathima, K.Hari Kishore, "Design of a Low Power and High Performance Digital Multiplier Using a Novel 8T Adder", International Journal of Engineering Research and Applications, ISSN: 2248-9622, Vol. 3, Issue.1, Jan-Feb., 2013.

- [26] Harikishore Kakarla, Madhavi Latha M and Habibulla Khan, "Transition Optimization in Fault Free Memory Application Using Bus-Align Mode", European Journal of Scientific Research, Vol.112, No.2, pp.237-245, ISSN: 1450-216x135/1450-202x, October 2013.

- [27] T. Padmapriya and V. Saminadan, "Improving Throughput for Downlink Multi user MIMO-LTE Advanced Networks using SINR approximation and Hierarchical CSI feedback", International Journal of Mobile Design Network and Innovation- Inderscience Publisher, ISSN: 1744-2850 vol. 6, no.1, pp. 14-23, May 2015.

- [28] S. V. Manikanthan and K.srividhya "An Android based secure access control using ARM and cloud computing" Published in: Electronics and Communication Systems (ICECS), 2015 2nd InternationalConferenceon 26-27Feb. 2015, Publisher: IEEE, <a href="https://doi.org/10.1109/ECS.2015.7124833">https://doi.org/10.1109/ECS.2015.7124833</a>.